非公開株式会社「Proton-Electrotex」製のパルス適用の大出力高圧サイリスタ

Anatoly Chernikov, Vladimir Goncharenko, Alexandr Mizintsev, Dmitry Titushkin and Alexey Surma

Proton-Electrotex, Orel, Russia,

NIIEFA-ENERGO, S.-Peterburg, Russia

数十キロアンペアから数百キロアンペアの範囲の短電流パルスをスイッチングできる半導体スイッチの開発は、強力な電気物理機器用のスイッチング電源の開発に関連しています。 インパルスサイリスタは、このようなキーとして広く使用されています[1]。

顧客は強力なインパルスサイリスタのために多くの特定の技術的要求を課します[2-5]。これは通常のシリアルサイリスタでは満たすことができません。こうした要件には、以下が含まれます

上昇率が1000アンペア/マイクロ秒以上の電流パルス発生。標準要求は2000~10000アンペア/マイクロ秒です。

高振幅の短い電流パルスの発生。発生されるパルスにおける電流の振幅のサイリスタの平均電流値に対する比率は100以上達することができます。

上昇率が速い電流パルスを作る際、並列装置の一部であるサイリスタの同期入力

電流上昇率(di/dt)が1000アンペア/マイクロ秒以上のパルスを発生する際、サイリスタ素子のスイッチオンが面積にわたり非同時であることに関連している重要な問題が発生します。

この問題の本質的な解決は、ゲートターンオフサイリスタ(GTO)と集積化ゲート転流型サイリスタ(IGCT)のために使用されるセル型多数エミッタタイプの位相幾何学のあるサイリスタの使用です[6]。なぜかというと、エミッタのそれぞれのセルの横幅のサイズが小さいため、サイリスタはほぼ同時に全面積にわたってスイッチオンするからです。ただし、このような機器の大部分(50% 以上)がゲートに占められ、電流を通す面積外となるので、電流パルスの許容振幅をかなり狭くします。

もう一つのソリューションとして、逆スイッチオンダイニスタという特別なパルス機器の適用も挙げられます[7]。機器のスイッチオンは同じく全面積にわたって行われ、半導体スイッチのために現在最大のパルス電流振幅に達成することができます[8]。欠点としては、逆スイッチオンダイニスタの始動に必要な複雑な器具が必要なことを指摘するべきです。その価格はメインスイッチの価格に相当します。

したがって、建設的技術的解決策の探求は適切であり、「伝統的な」パルスサイリスタの許容インパルス電流を増加させることを可能にします。 以下は、実用的な応用にとって重要な100~1000マイクロ秒の範囲内の極めて高い振幅を有する電流パルスをスイッチングすることができるパルスサイリスタを作り出すことを可能にした一組の技術的解決策です。

構造および製造技術の特徴

半導体装層

半導体素子において割と低合金p-ベースがあります(n-エミッタの下の層抵抗は500~1000オム毎スクウェア)。また、ベースを形成する拡散過程は、層内に最大限の「内蔵圧延電界」が得られるように最適化されています。そのおかげで、n-エミッタから注入された電子がp-ベースを通る時間を最小限にして、ターンオン時間のディレイの最低値を得ることができます。従って、カスケード入力(補助サイリスターメインサイリスタ)の場合、補助サイリスタのみ電流を通す時間が最低値となり、di/dt安定性が本質的に増加します。従って、並列装置のサイリスタのターンオンディレイのばらつきを非常に低下させることが可能です。

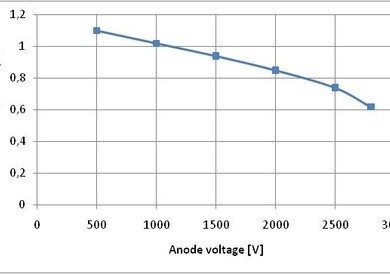

図1で実験用サイリスタの場合、ターンオン時間のディレイと当初ロック電圧の古典的依存が表示されています。

(b)

図1.ターンオン時間のディレイとアノード電圧の古典的な依存。制御電流の上昇率は2アンペア/マイクロ秒で、アノード電流の上昇率は5000アンペア/マイクロ秒です。

ターンオン遅延時間は絶対値が小さいだけでなく、アノード電圧の増加とともに単調に減少することがわかります。これは、初期アノード電圧の増加に伴うサイリスタのベース層を通る電荷キャリアの飛行時間の減少によって説明されます。

このようなオン遅延時間の依存性は、直列接続されたサイリスタの動作中のオン時間の広がりの「収束」につながります。 シリアルアセンブリ内の個々のサイリスタのスイッチング時間の広がりにより、スイッチオンの初期段階でサイリスタ間の電圧が再分配されます。 tの値が小さいサイリスタの場合、アノード電圧が低下し、tの値が大きいサイリスタでは 増加します。

また、t数値は 並列装置において、個別のサイリスタで測定された数値に比べて、電圧との依存(図1)によって低下したり、増大したりします。つまり、サイリスタの並列接続において、接続に入っているそれぞれの個別サイリスタに比べて、ターンオンディレイ数値のばらつき範囲は狭くなります。

研究[9]によると、Proton-Electrotex社製のパルスサイリスタの古典的なt数値とアノード電圧との消極的な依存の場合、t数値のばらつきは 並列接続において約2倍少なくなります。

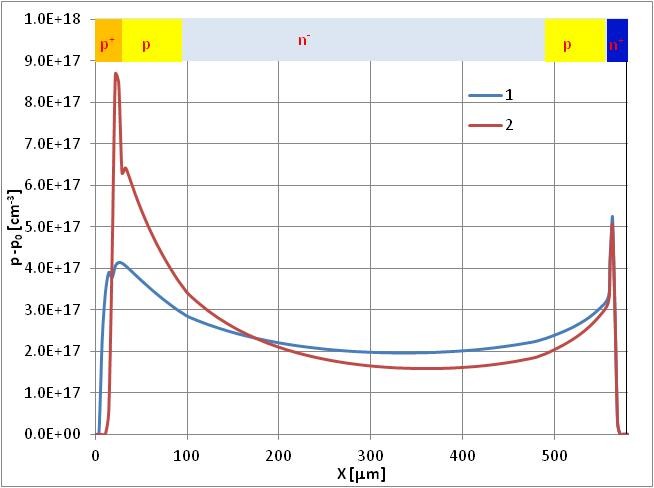

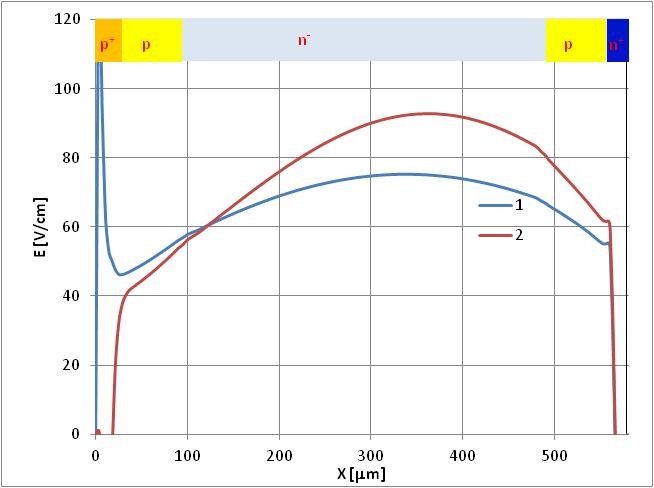

・コントロールできる効率性のあるエミッタ

「従来の」パワーサイリスタの半導体素子では、n層の厚さ(Wn)とこの層の電子正孔対の両極性拡散長(L)の比は少なくとも3(Wn / L> 3)です。この比率は、必要なブロッキング電圧とdu / dt抵抗を提供するために、4層サイリスタ構造の一部として、p-n-pトランジスタの明確な(高電圧で約0.8で)電流ゲインを必要とするためです。ただし、この場合、オン状態では、過剰な電子正孔対の濃度の構造の厚さにわたる分布は実質的に不均一であり、その結果、電界強度の分布も不均一になります(図2を参照)。

Proton-Electrotex社製のパルスサイリスタにおいて、p-n-pトランジスタの電流増幅係数の必要な数値を維持するために、特別な構成のp-エミッタ、つまり透明なエミッタ(transparent emitter)を使います。それを形成する拡散技術とアノードのオーム接触の低温形成技術(焼結)は、高度の再生性で注入係数を制御し、電力半導体構造の全面積にわたるばらつきを少なくすることを可能にします。

コントロールできる効率性のあるp-エミッタを使うことで、Wn対Lの比率を1以下まで下げることができます。その結果、構造の厚さにわたる電界の電圧はより均等になります(図2)。

バルク損失電力密度は、電界強度と電流密度の積ですから、制御された効率のpエミッターを持つ構造の場合、同じ電圧降下を持つ従来のサイリスタの構造よりも、局所損失電力密度(および損失エネルギー密度)が低くなります。放熱プロセスが断熱的と見なされる短い電流パルスの場合、これにより、効率が制御されたpエミッターを持つ構造体の局所的な過熱が約 20% パーセント少なくなります。 したがって、エネルギーの場合は、この構造的および技術的ソリューションの使用により、オン状態で同一のI-V特性を持つ「従来の」サイリスタと比較して、高振幅の短い電流パルスをスイッチングするときの許容損失エネルギーで最大20% の利点を得ることができます。

高度分岐の制御電極

高度分岐の制御電極 お蔭で、高スルーレートで安全に電流パルスを切り替え、アクティブ領域全体でサイリスタ構造をすばやくオンにすることができます。

適用されるトポロジと達成可能なインパルス特性を表1に示します。各直径のサイリスタ素子について、2つのトポロジのバリエーションが開発され、実際に使用されています。「最大」分岐と「最適」分岐です。最大分岐のタイプは、最高スルーレートのスイッチング電流パルス用に設計されていますが、制御電極の配置に大きな面積損失があるため、パルス持続時間が200 ... 300μsを超える電流パルスの許容振幅の2番目のオプションよりも劣っています。 「最適分岐」のタイプは、300μsを超える期間の最大振幅の電流パルスをスイッチングするために最適化されています。このトポロジは、3〜8 kA /μsのスルーレートで電流パルスをスイッチングするときに、半導体構造の領域全体での損失エネルギー密度と過熱温度の広がりが重要でないように設計されています。

分配型補助サイリスタ

シリコン要素の面積が大きい最新のサイリスタの設計には、通常、分岐制御電極(BCE)と補助(増幅)サイリスタ(BT)が含まれ、そのカソードはBCEに接続され、アノードはメインサイリスタ構造と共通です。 BTの目的は、BCEに供給される「強化された」制御電流パルスを形成することです。通常、BT構造は、サイリスタの主制御電極を囲む幅約1 mmのやや狭いリングの形で形成されます。サイリスタが通常モードで機能するには、 BCEの周囲に沿ってメインサイリスタをオンにした後、アノード電流はすぐに「遮断」され、VTがオフになるか、その電流密度が「安全な」制限まで減少するから、これで十分です。

ただし、1000 A / µsを超えるスルーレートで電流パルスをスイッチングすると、HTを流れる電流密度の低下が非常に遅くなり、電流振幅が大きな値に達する可能性があることが研究により示されています。

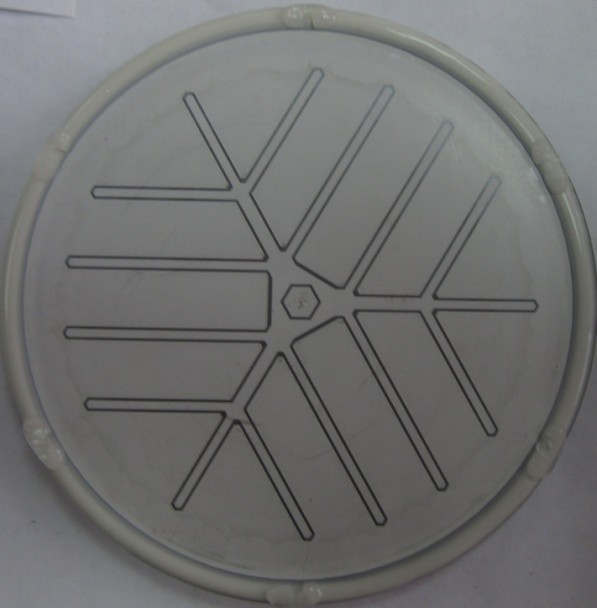

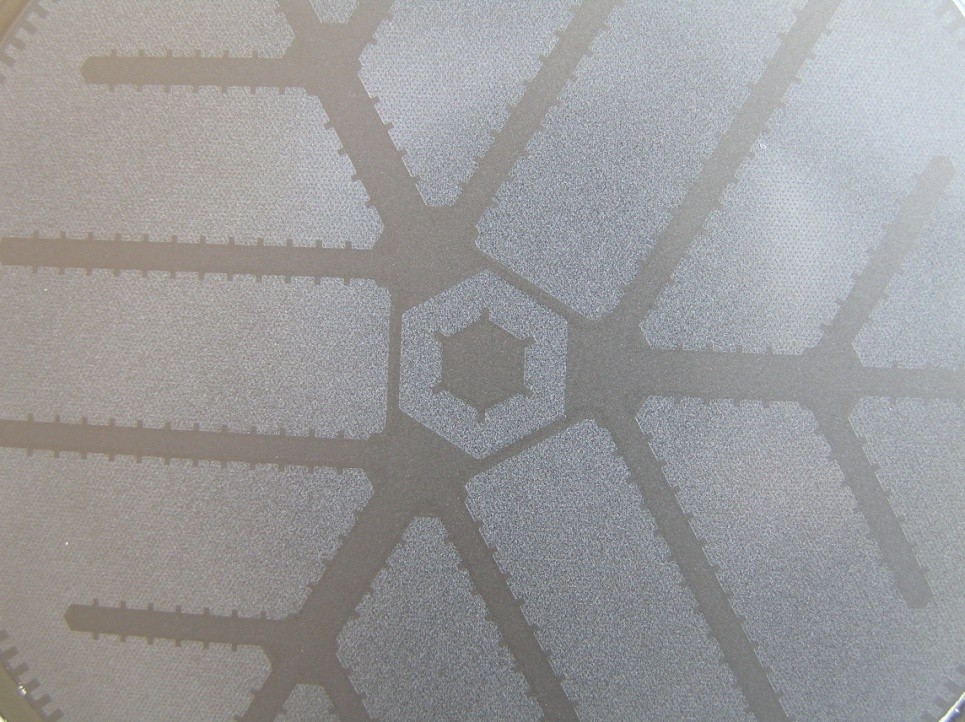

BTの構造を「アンロード」させるため、つまりBTを流れる電流の密度を下げるために、Proton-Electrotex社製パルスサイリスタでは、直径56 mmの要素の場合、約0.5平方cmの面積、または直径が80〜100 mmの要素の場合、約1〜2平方メートルの面積を持つ「完全なサイリスタ構造」である分散型BTが使用されます 。 (図5)。研究により、このようなBT構造を使用すると、この構造の局所的な過熱を、主構造の最大過熱よりも低い値に減らすことができることが示されています。

分散BTおよび細かいカソードバイパス付きのパルスサイリスタのシリコン素子

細かいカソードバイパス

基本シャントサイズが約100μmのnエミッターの分散型カソードシャントを使用されました。 nベースの電子正孔対の両極性拡散長の典型的な値は約400ミクロンです。 したがって、このようなシャントの使用により、カソードシャントの位置の下に局所的な「くぼみ」のない過剰電子正孔対の濃度の均一な分布を得ることができ、サイリスタ構造のアクティブ領域全体を使用して電流を伝導します。

半導体構造のアノードと熱補正器のモリブデンディスクとのコンタクト

半導体構造のアノードと熱補正器のモリブデンディスクとのコンタクト 低温焼結技術を使用して、細かく分散した銀ペーストの層上で実行されます(焼結)[10]。 この技術は、銀ペーストを実際にモノリシックな銀に低温(約250°C)で焼結する工程です。 パルスサイリスタの場合は、次の利点があります。・過程は250°Cで進みますが、モリブデンディスクとの接合のために使われる焼結過程(シルミンの上の真空接合)は約700°Cで行われます。そのため、焼結後、シリコン・モリブデンパッケージのほうが、残変形及び内部機械的<<がずっと小さいです。 その結果、サイクル抵抗[11-12]の観点からリソースが増加します(必要な振幅の電流スイッチングモードでは、この特徴は重要です。なぜなら、 シリコンに隣接する浅い層を除いて、200°C以上の温度でモリブデンディスクは低温のままになるからです。・従来の融合プロセスでは、シリコン構造の表面層がシルミンによって溶解されます。 その場合には、(従来の「半透明でない」pエミッタであっても)構造の領域全体にわたってアノードエミッタの特性の同一性を保証することが不可能になります。 その結果、従来の技術では、構造の領域全体で電流密度の広がりが大きくなりました。 焼結技術はこの欠点を解消します[13]。

非常に難しいです。特に、面積が広い場合はそうです。その結果、シルミンの結晶化は、通常周辺から始まり、ディスク型のシリコン・モリブデンパッケージの中央に向けて進みます。それは、直径に沿った継ぎ目の厚さの不均等性に繋がります

圧入カソード接触

信頼性の高いクランプ陰極接点を確保するために、特別なコーティングが施されたモリブデン陰極パッドが使用されます。 これは、さまざまな材料とコーティングの長時間にわたる膨大な研究の結果としての選択です。 使用されるガスケットは、高い接触抵抗、低い電気抵抗および熱抵抗を提供し、多数の(100,000を超える)高振幅電流パルスをスイッチングする場合を含む長期動作中に劣化しません。

上記の構造的および技術的解決策は知られており、多くの製造業者によってサイリスタのパルス特性を改善するために個別に使用されています。しかし、Proton-Electrotex社が最新の技術的能力を考慮して適用されたこれらの技術的ソリューションの全体によって、ユニークな特性セットを持つパルスサイリスタの連続生産が可能になりました。例として、半導体素子の直径が100 mmのクラス28サイリスタの連続アセンブリに基づく実験的なパルススイッチのテスト結果を以下に示します[14]。

パルスサイリスタに基づく実験スイッチ

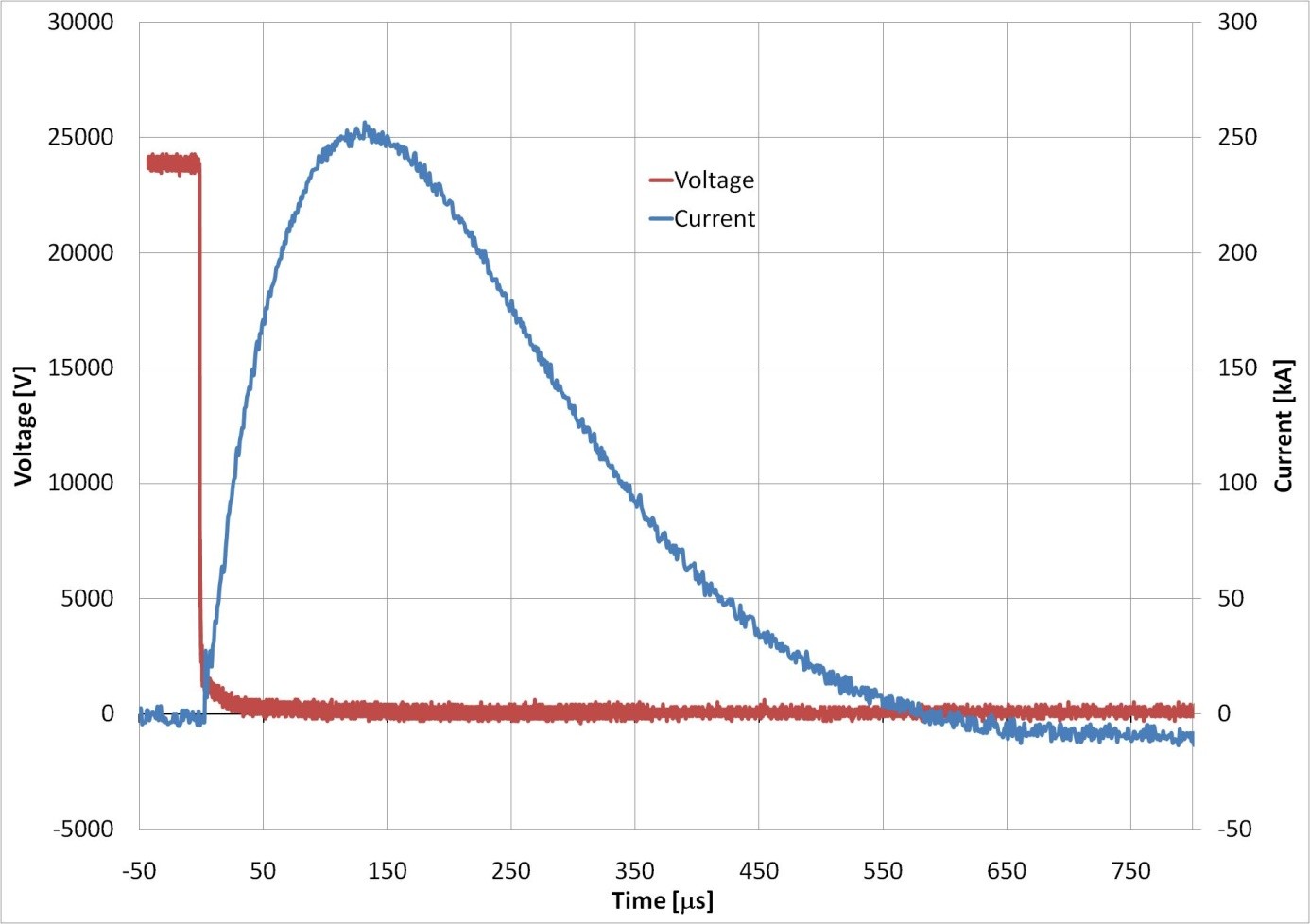

上記の技術的ソリューションを使用して、2800 Vの繰り返しパルスブロッキング電圧を持つ実験パルスサイリスタを製造しました。サイリスタには、抵抗率120 Ω* cm、厚さ580μmの中性子ドープシリコンウェーハ上に製造された直径100 mmのシリコン要素がありました。制御電極のトポロジーは表1(5頁)をご覧ください。このトポロジは、グパルスの形状が正弦波の半波に近く、300〜1000μsの長さがあるスイッチンに接続する場合、エリア全体で最適なサイリスタのターンオン時間を提供します。 この場合、制御領域を配置するための領域の損失は最小限に抑えられ、約 14%, になります。サイリスタ素子の有効領域は約55 cmです。実験用のサイリスタスイッチ(図7)は、直列サイリスタ10個および、逆並列ダイオードの補助装置からなりました。

実験用のサイリスタスイッチ

実験はR-L-C放電回路(図8)で行われました。コンデンサの当初電圧は24キロワットでした。電流パルスと放電における電圧の形は図9で表示されています。実験中、スイッチは、250キロアンペアまでの振幅と約4,5キロアンペア/マイクロ秒の電流上昇率の電流パルスを安定的に作ります。

アノード電流とサイリスタスイッチの電圧

分枝型制御電極のトポロジー

Топологии разветвленного управляющего электрода

|

№ |

素子直径、ミリメートル |

トポロジーの種類 |

許容di/dt、アンペア/マイクロ秒 |

タイプ・完全オン時間、マイクロ秒 |

I2t, А2с |

|

1 |

56 |

|

4000(底辺100マイクロ秒の台形パルス、振幅10キロアンペア) |

40…60 |

3,0E6 (UDRM=2800 В) 1,8E6 (UDRM=4400 В) Tj=25C, 10ミリ秒、正弦波の半波 |

|

2 |

56 |

|

6000(底辺100マイクロ秒の台形パルス、振幅10キロアンペア) |

20…30 |

2,3E6 (UDRM=2800 В) 1,4E6 (UDRM=4400 В) Tj=25C, 10ミリ秒、正弦波の半波 |

|

3 |

80 |

|

6000(底辺100マイクロ秒の台形パルス、振幅20キロアンペア) |

40…60 |

17,0E6 (UDRM=2800 В) 10,0E6 (UDRM=4400 В) Tj=25C, 10ミリ秒、正弦波の半波 |

|

4 |

80 |

|

10000 底辺100マイクロ秒の台形パルス、振幅20キロアンペア) |

20…30 |

10,0E6 (UDRM=2800 В) 6,0E6 (UDRM=4400 В) Tj=25C, 10ミリ秒、正弦波の半波 |

|

5 |

100 |

|

10000 底辺100マイクロ秒の台形パルス、振幅20キロアンペア) |

40…60 |

37,0E6 (UDRM=2800 В) 24,0E6 (UDRM=4400 В) Tj=25C, 10ミリ秒、正弦波の半波 |

|

6 |

100 |

|

15000 底辺100マイクロ秒の台形パルス、振幅20キロアンペア) |

20…30 |

26,0E6 (UDRM=2800 В) 16,0E6 (UDRM=4400 В) Tj=25C, 10ミリ秒、正弦波の半波 |

文献

[1] M.E.Savage "Final Results From the High-Current, High-Action Closing Switch Test Program at Sandia National Laboratories", IEEE Transactions on Plasma Science, vol. 28, no. 5, pp. 1451-1455, Oct. 2000.

[2] H. Singh and C. R. Hummer “High action thyristors for pulse power applications”, in 12th IEEE Pulse Power Conference, June 1999.

[3] S. Ikeda and T. Araki, “ The di/dt capability of thyristors”, Proc. IEEE, no. 8, pp. 1301-1305, 1967.

[4] S.S. Asina, A.M. Surma, “A new design-technology technique for optimization of high power pulse thuristor characteristics”, in ELECTRIMACS Conference, Saint-Nazaire, Sept. 1996, pp. 485-490.

[5] W.H. Tobin, “Effect of gate configuration on thyristor plasma properties”, in IEE IAS Conference Record, IEE IAS Annual Meeting, 1978.

[6] Linder S., Klaka S. et al., "A New Range of Reverse Conducting Gate-Commutated Thyristors for High Voltage, Medium Power Applications", in EPE'97 Conference, pp. 1.117 - 1.124. 1997.

[7] A. V. Gorbatyuk, I. V. Grekhov, and A. V. Nalivkin, "Theory of quasidiode operation of reversely switched dinistors", Solid-State Electron., vol. 31 , pp. 1483-1491, 1988.

[8] S A. Belyaev, V.G. Bezuglov et al., “New Generation of High – Power Semiconductor Closing Switches for Pulsed Power Applications” in ICPIG Conference, Prague, July 2007.

[9] 1. H. Schwarzbauer, “Novel Large Area Joining Technique for Improved Power Device Performance”, IEEE Transactions on Industrial Applications, 27 (1), 1991, p. 93- 95.

[10] Amro R.; Lutz J. et al. “Power Cycling at High Temperature Swings of Modules with Low Temperature Joining Technique”, in ISPSD Conference, Naples, 2006.

[11] C. Göbl, P. Beckedahl, H. Braml, “Low temperature sinter technology Die attachment for automotive power electronic applications” in Automotive Power Electronics Conference, Paris, June 2006, pp. 2-5.

[12] D. Titushkin, A. Surma, “New ways to produce fast power thyristors”, Bodo’s Power Systems 08, 2015, p. 28- 29.